Most Commented

VHDL for an FPGA Engineer with Vivado Design Suite

Description material

6.97 GB | 25min 56s | mp4 | 1920X1080 | 16:9

Genre:eLearning |Language:English

Files Included :

1 - Agenda.mp4 (2.25 MB)

2 - How to Download Install Vivado Design suite and add License.mp4 (65.54 MB)

4 - How to verify License Installation.mp4 (23.22 MB)

5 - Adding boards such as Nexys 4 DDR which are not available in the Vivado.mp4 (21.41 MB)

103 - Target.mp4 (5.02 MB)

104 - Half adder.mp4 (8.39 MB)

105 - Full adder with Half adder.mp4 (164.97 MB)

107 - Using Vivado IP Integrator 4bit Ripple Carry adder.mp4 (117.99 MB)

109 - Johnson Counter with D FlipFlop.mp4 (150.59 MB)

110 - Target.mp4 (18.82 MB)

111 - State Machines.mp4 (6.91 MB)

112 - Mealy FSM Three Process Methodolgy.mp4 (83.94 MB)

114 - Mealy FSM Two Process Methodology.mp4 (18.05 MB)

116 - Mealy FSM SIngle Process Methodology.mp4 (23.29 MB)

118 - Moore FSM Three Process Methodology.mp4 (76.31 MB)

120 - Moore FSM Two Process Methodology.mp4 (15.47 MB)

122 - Moore FSM Single Process Methodology.mp4 (18.68 MB)

124 - Understanding Sequence Detector.mp4 (23.49 MB)

125 - Implementing Overlapping Sequence Detector.mp4 (101.07 MB)

127 - Traffic Light Controller Flowchart.mp4 (8.27 MB)

128 - Understanding Traffic Light Controller.mp4 (95.06 MB)

130 - What are alternatives to generate stimulis for Sequence detector Bishal.mp4 (154.49 MB)

132 - Target.mp4 (10.17 MB)

133 - How we Create IP.mp4 (133.62 MB)

134 - How we refresh IP repository.mp4 (61.83 MB)

135 - How we add Customization Parameters to IP.mp4 (73.02 MB)

136 - Complete Design P1 Barrel Shifter.mp4 (28.76 MB)

137 - Complete Design P2.mp4 (126.54 MB)

138 - Undertanding ILA and VIO.mp4 (101.37 MB)

139 - Adding ILA core to design.mp4 (138.85 MB)

141 - Analyzing Waveform with ILA.mp4 (13.09 MB)

142 - Adding Virtual IO core to the design.mp4 (147.71 MB)

144 - Analyzing response of the System with VIO.mp4 (12.93 MB)

145 - Understanding Memories in FPGA.mp4 (66.03 MB)

146 - Distributed Memory Vs Block Memory.mp4 (44.76 MB)

148 - Creating Memory Method 1.mp4 (71.05 MB)

149 - Creating Memory Method 2.mp4 (104.08 MB)

150 - Creating Memory Method 3.mp4 (108.82 MB)

151 - Single Port RAM with Block Memory.mp4 (76.53 MB)

153 - Single Port RAM with Distributed Memory.mp4 (64.09 MB)

155 - Single Port ROM IP with Block Memory and COE file.mp4 (75.13 MB)

156 - Signle Port RAM in VHDL with Testbench.mp4 (324.04 MB)

157 - Project Categories.mp4 (2.89 MB)

158 - Implementation of VGA Controller in VHDL.mp4 (172.09 MB)

160 - P1 Implementing 4bit Barrel Shifter with Rotate Logic.mp4 (217.25 MB)

162 - P2 Implementation of Universal Serial Asynchronus TransmitterUART with VHDL.mp4 (198.54 MB)

164 - Implementation of SPI for DAC PMOD DA4 in VHDL.mp4 (299.12 MB)

167 - Need of Reprogrammable architecture.mp4 (17.06 MB)

168 - PLD Classification.mp4 (6.19 MB)

169 - Understanding Programmable Logic in PROM.mp4 (17.74 MB)

170 - PROM Demonstration on NI Multisim IDE.mp4 (52.09 MB)

171 - PAL and PLA.mp4 (9.64 MB)

172 - SPLD and GAL.mp4 (10.28 MB)

173 - Understanding GAL Datasheet 16V8.mp4 (17.88 MB)

174 - SPLD and GAL Summary.mp4 (11.47 MB)

175 - CPLD architecture.mp4 (33.36 MB)

176 - Introduction to FPGA Architecture.mp4 (19.68 MB)

177 - Use of Wide Multiplexer.mp4 (14.41 MB)

178 - Spartan 6 Architecture.mp4 (58.43 MB)

179 - Spartan 6 FPGA Architecture Summary.mp4 (11.83 MB)

10 - User Programmable IO of FPGA vs MCU.mp4 (4.21 MB)

11 - Comparing Temporary storage.mp4 (15.79 MB)

12 - Whether Coding Guidlines really matters.mp4 (75.07 MB)

13 - How to buy FPGA board in India without paying Custom duty and GSTN no.mp4 (33.59 MB)

7 - Agenda.mp4 (2.69 MB)

8 - Demonstration of Parallel architecture usage.mp4 (26.64 MB)

9 - Ease of working with FPGAs.mp4 (47.01 MB)

15 - Agenda.mp4 (3.04 MB)

16 - Design Flow P1.mp4 (35.46 MB)

17 - Design Flow P2.mp4 (53.13 MB)

18 - Design Flow P3.mp4 (87.22 MB)

19 - Design flow P4.mp4 (65.34 MB)

20 - Design Flow P5.mp4 (67.07 MB)

21 - Summary of Design Flow.mp4 (29.8 MB)

22 - First Look at VHDL Code.mp4 (69.57 MB)

23 - Insights P1.mp4 (40.56 MB)

24 - Insights P2.mp4 (18.35 MB)

27 - Agenda.mp4 (5.96 MB)

28 - Understanding IO Planning Project.mp4 (44.85 MB)

29 - Understanding Synthesis Settings.mp4 (50.7 MB)

34 - Understanding Implementation Strategies of VIVADO.mp4 (93.09 MB)

36 - Complete FPGA Design Flow P1.mp4 (40.93 MB)

37 - Complete Design flow P2.mp4 (112.22 MB)

39 - Agenda.mp4 (4.58 MB)

40 - Fundamentals Signal and Variable P1.mp4 (23.06 MB)

41 - Fundamentals Signal and Variable P2.mp4 (8.16 MB)

42 - Format of Signal and Variable.mp4 (8.97 MB)

43 - Datatypes in VHDL.mp4 (4.31 MB)

44 - Using Builtin datatype.mp4 (28.37 MB)

45 - Using Nonbuiltin datatypes.mp4 (11.92 MB)

46 - Using User defined datatypes.mp4 (8.4 MB)

47 - Using Signal.mp4 (42.69 MB)

48 - Using Variable.mp4 (27.93 MB)

49 - Initialization of Variable.mp4 (18.08 MB)

50 - Agenda.mp4 (8.77 MB)

51 - Different Modeling Style.mp4 (29.41 MB)

52 - Dataflow Modeling Style Fundamentals.mp4 (7.27 MB)

53 - Operators in Dataflow Modeling Style.mp4 (14.69 MB)

54 - Assignment Operator in Dataflow Modeling Style.mp4 (9.21 MB)

55 - Implementation of Half adder.mp4 (29.81 MB)

56 - Implementation of Full adder.mp4 (87.63 MB)

57 - Handling Multibit vectors P1.mp4 (38.53 MB)

58 - Handling Multibit vectors P2.mp4 (16.64 MB)

59 - Shift Operators Fundamentals.mp4 (39.62 MB)

60 - Shift Operator Demonstration.mp4 (99.74 MB)

61 - Rotation Operator Fundamentals.mp4 (6.59 MB)

62 - Rotation Operator Demonstration.mp4 (30.99 MB)

63 - Arithmetic Operator Fundamentals.mp4 (13.59 MB)

64 - Arithmetic Opertation Unsigned Type.mp4 (55.85 MB)

65 - Arithmetic Opertation StdlogicVector Type.mp4 (57.17 MB)

66 - Understanding typeconversion function.mp4 (28.23 MB)

67 - typeconversion Demonstration.mp4 (52.21 MB)

68 - Conditional and Selected Signal Statement.mp4 (9.83 MB)

69 - Conditional and Selected Signal Statement.mp4 (108.51 MB)

70 - Agenda.mp4 (2.7 MB)

71 - Understanding Process block.mp4 (12.65 MB)

72 - Behavioral Modeling Style Skeleton.mp4 (15.48 MB)

73 - Understanding IF ELSE P1.mp4 (20.59 MB)

74 - Understanding IF ELSE P2.mp4 (38.98 MB)

75 - Good Practices IF ELSE P1.mp4 (31.03 MB)

76 - Good Practices IF ELSE P2.mp4 (18.9 MB)

77 - DFlipflop with Synchronus Reset.mp4 (27.21 MB)

78 - DFlipflop with Asynchronus Reset.mp4 (9.85 MB)

79 - Simulation Asynchronus Reset DFlipflop.mp4 (15.24 MB)

80 - Simulation Synchronus Reset DFlipflop.mp4 (18.99 MB)

81 - Case Statement Skeleton.mp4 (2.33 MB)

82 - 41 Mux with Case Statement.mp4 (18.31 MB)

83 - Binary to Seven Segment Decoder P1.mp4 (24.14 MB)

84 - Binary to Seven Segment Decoder P2.mp4 (118.01 MB)

85 - Binary to Seven Segment Decoder P3.mp4 (14.31 MB)

86 - Implementing Counter.mp4 (99.94 MB)

88 - Right Circular Shifter P1.mp4 (20.6 MB)

89 - Right Circular Shifter P2.mp4 (73 MB)

100 - Example 1 4bit Counter.mp4 (94.83 MB)

102 - Example 2 Adder IP.mp4 (150.94 MB)

91 - Ways to create Testbenches.mp4 (10.44 MB)

92 - Using Force Constant and Force Clock.mp4 (49.7 MB)

93 - VHDL TB Fundamentals P1 Testbench Overview.mp4 (45.43 MB)

94 - VHDL TB Fundamentals P2 Generating Random signals.mp4 (51.43 MB)

96 - VHDL TB Fundamentals P3 Generating Clock Signal.mp4 (27.19 MB)

98 - Summary.mp4 (13.85 MB)]

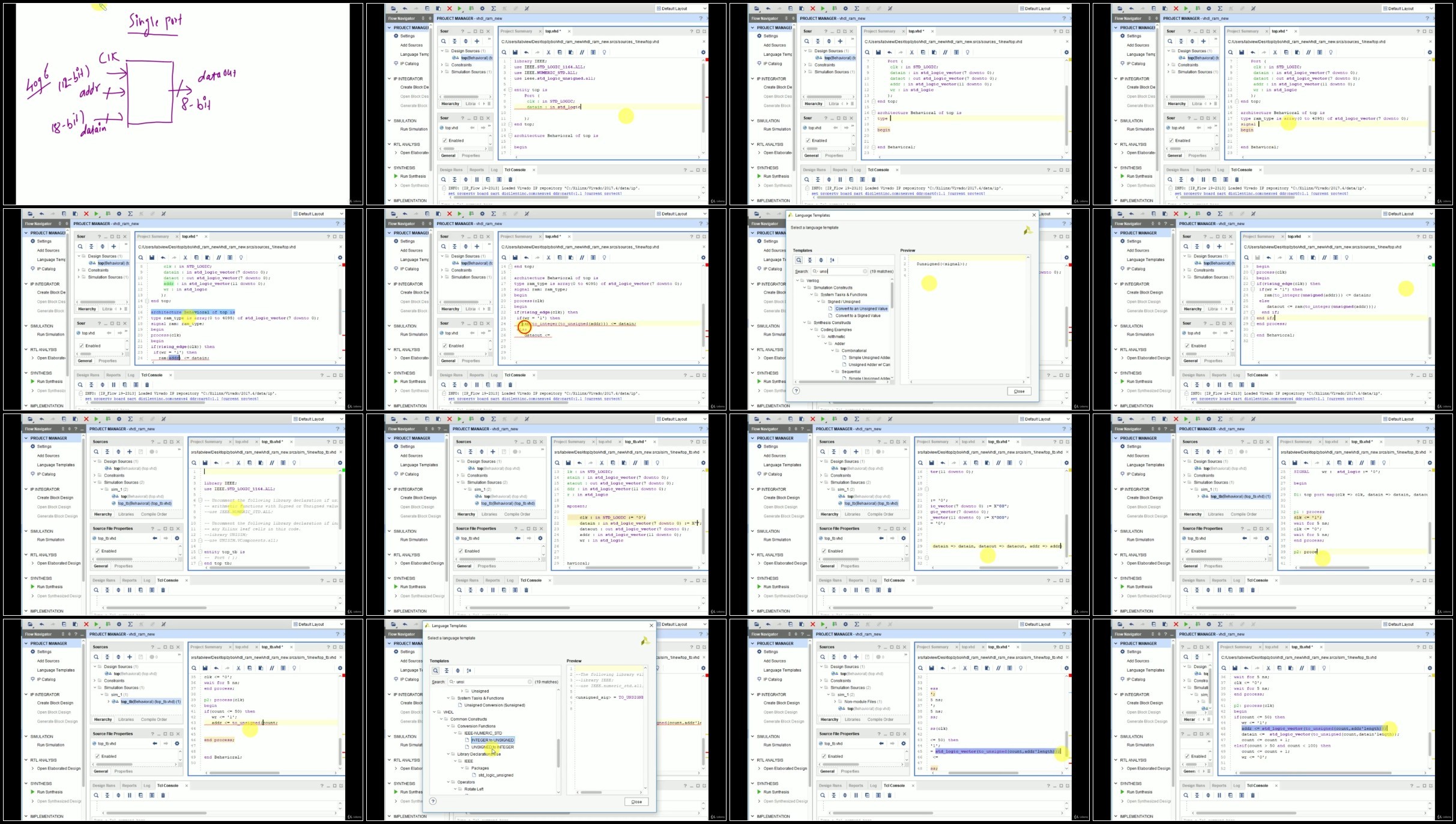

Screenshot

https://fikper.com/dtYVMadYxi/

https://fikper.com/2oU7zlqnz7/

https://fikper.com/00IEhIcwGY/

https://fikper.com/bKJItRPAd5/

https://rapidgator.net/file/37eca9aedc4a8a34d2c3a3fa4223243b/

https://rapidgator.net/file/39ef78b2fe239c561f3a11cfa344c69f/

https://rapidgator.net/file/70d790e5effb2b66336d92a993f05cf5/

https://rapidgator.net/file/dd5b5face5b0c3312822d6e16229c3c8/

https://nitroflare.com/view/53F23AACA2A239C/

https://nitroflare.com/view/8216F979730CDF4/

https://nitroflare.com/view/C9205BD9C921D01/

https://nitroflare.com/view/B7BF8E99F90E1EB/

Join to our telegram Group

Information

Users of Guests are not allowed to comment this publication.

Users of Guests are not allowed to comment this publication.

Choose Site Language

Recommended news

Commented

![eM Client Pro 9.2.1735 Multilingual [Updated]](https://pikky.net/medium/wXgc.png)

![Movavi Video Editor 24.0.2.0 Multilingual [ Updated]](https://pikky.net/medium/qhrc.png)